SLLS114 - D2433, JANUARY 1979 - REVISED MAY 1990

- Meets EIA Standard RS-422-A

- Operates From a Single 5-V Supply

- TTL Compatible

- Complementary Outputs

- High Output Impedance in Power-Off Conditions

- Complementary Output Enable Inputs

### description

The AM26LS31C is a quad complementaryoutput line driver designed to meet the requirements of EIA Standard RS-422-A Federal Standard 1020. The 3-state outputs have high-current capability for driving balanced lines such as twisted-pair or parallel-wire transmission lines, and they provide a high-impedance state in the power-off condition. The enable function is common to all four drivers and offers the choice of an active-high or active-low enable input. Low-power Schottky circuitry reduces power consumption without sacrificing speed.

The AM26LS31C is characterized for operation from 0°C to 70°C.

#### D OR N PACKAGE (TOP VIEW)

|                                      |                       |                            | _             |

|--------------------------------------|-----------------------|----------------------------|---------------|

| 1A [<br>1Y [<br>1Z [<br>2Z [<br>2Y [ | 2<br>3<br>4<br>5<br>6 | 15<br>14<br>13<br>12<br>11 | 4Z<br>G<br>3Z |

| 2A [                                 | 7                     | 10                         | [] 3Y         |

| 2A 🛚                                 |                       |                            |               |

| GND [                                | 8                     | 9                          | ] 3A          |

|                                      |                       |                            |               |

# FUNCTION TABLE (each driver)

| INPUT | ENA | BLES | OUTPUTS |     |  |  |

|-------|-----|------|---------|-----|--|--|

| Α     | G   | G    | Y       | Z   |  |  |

| I     | н   | Х    | Н       |     |  |  |

| L     | H   | X    | L       | Н   |  |  |

| Н     | X   | L    | н       | / L |  |  |

| L     | X   | L    | L       | н   |  |  |

| X     | L   | н    | Z       | z   |  |  |

H = high level L = low level X = irrelevant

Z = high impedance (off)

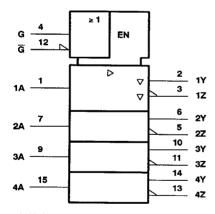

# logic symbol†

<sup>†</sup> This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

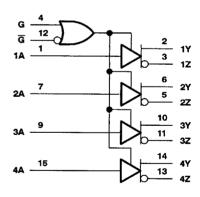

### logic diagram (positive logic)

PRODUCTION DATA information is current as of publication date Products conform to specifications per the terms of Texas instrument, standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1990, Texas Instruments Incorporated

POST OFFICE BOX 655303 \* DALLAS, TEXAS 75265

2-13

8961724 0090257 6T1 **=**

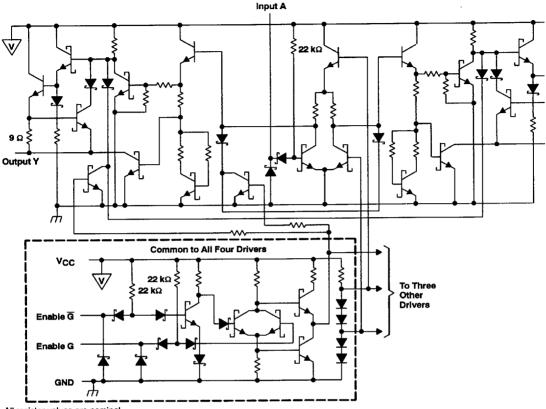

#### schematic (each driver)

All resistor values are nominal.

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, V <sub>CC</sub> (see Note 1)                 | 7 V                          |

|--------------------------------------------------------------|------------------------------|

| Input voltage, V <sub>I</sub>                                |                              |

| Output offstate voltage                                      | 5.5 V                        |

| Continuous total power dissipation                           | See Dissipation Rating Table |

| Operating free-air temperature range, T <sub>A</sub>         | 0°C to 70°C                  |

| Storage temperature range                                    | 65°C to 150°C                |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds | 260°C                        |

NOTE 1: All voltage values, except differential output voltage VOD, are with respect to network ground terminal.

#### DISSIPATION RATING TABLE

| PACKAGE | T <sub>A</sub> ≤ 25°C<br>POWER RATING | DERATING FACTOR<br>ABOVE TA = 25°C | TA = 70°C<br>POWER RATING |  |  |

|---------|---------------------------------------|------------------------------------|---------------------------|--|--|

| D       | 950 mW                                | 7.6 mW/°C                          | 608 mW                    |  |  |

| N       | 1150 mW                               | 9.2 mW/°C                          | 736 mW                    |  |  |

2-14

POST OFFICE BOX 655303 \* DALLAS, TEXAS 75265

8961724 0090258 538

#### recommended operating conditions

|                                          | MIN  | NOM | MAX  | UNIT |

|------------------------------------------|------|-----|------|------|

| Supply voltage, V <sub>CC</sub>          | 4.75 | 5   | 5.25 | ٧    |

| High-level input voltage, VIH            | 2    |     |      | ٧    |

| Low-level input voltage, V <sub>IL</sub> |      |     | 0.8  |      |

| High-level output current, IOH           |      |     | -20  | mA   |

| Low-level output current, IOL            |      |     | 20   | mA   |

| Operating free-air temperature, TA       | 0    |     | 70   | ů    |

# electrical characteristics over operating free-air temperature range (unless otherwise noted)

| PARAMETER      |                                                 | TEST CONDITIONS                       |                         | MIN | TYP | MAX   | UNIT |

|----------------|-------------------------------------------------|---------------------------------------|-------------------------|-----|-----|-------|------|

| ViK            | Input clamp voltage                             | V <sub>CC</sub> = 4.75 V,             | l <sub>I</sub> = -18 mA |     |     | -1.5  | V    |

| Voн            | High-level output voltage                       | V <sub>CC</sub> = 4.75 V,             | IOH = -20 mA            | 2.5 |     |       | ٧    |

| VOL            | Low-level output voltage                        | V <sub>CC</sub> = 4.75 V,             | IOL = 20 mA             |     |     | 0.5   | ٧    |

| loz            | Off-state (high-impedance state) output current | V <sub>CC</sub> = 4.75 V              | V <sub>O</sub> = 0.5 V  |     |     | -20   | μА   |

|                |                                                 |                                       | V <sub>O</sub> = 2.5 V  |     |     | 20    |      |

| l <sub>l</sub> | Input current at maximum input voltage          | V <sub>CC</sub> = 5.25 V,             | V <sub>I</sub> = 7 V    |     |     | 0.1   | mA   |

| lн             | High-level input current                        | V <sub>CC</sub> = 5.25 V <sub>i</sub> | V <sub>I</sub> = 2.7 V  |     |     | 20    | μA   |

| liL.           | Low-level input current                         | V <sub>CC</sub> = 5.25 V,             | V <sub>I</sub> = 0.4 V  |     |     | -0.36 | μΑ   |

| los            | Short-circuit output current‡                   | V <sub>CC</sub> = 5.25 V              |                         | -30 |     | -150  | mA   |

| Icc            | Supply current                                  | V <sub>CC</sub> = 5.25 V,             | All outputs disabled    |     | 32  | 80    | mA   |

<sup>&</sup>lt;sup>†</sup> All typical values are at  $V_{CC} = 5 \text{ V}$  and  $T_A = 25^{\circ}\text{C}$ .

# switching characteristics, $V_{CC} = 5 \text{ V}$ , $T_A = 25^{\circ}\text{C}$

| PARAMETER        |                                                     | TEST CONDITIONS                                         |                         | MIN | TYP | MAX | UNIT |

|------------------|-----------------------------------------------------|---------------------------------------------------------|-------------------------|-----|-----|-----|------|

| <sup>t</sup> PLH | LH Propagation delay time, low-to-high-level output |                                                         |                         |     | 14  | 20  | ns   |

| <sup>t</sup> PHL | Propagation delay time, high-to-low-level output    | C <sub>L</sub> = 30 pF, S1 and S2 open,<br>See Figure 1 | S1 and S2 open,         |     | 14  | 20  | ns   |

|                  | Output-to-output skew                               |                                                         |                         | 1   | 6   | ns  |      |

| <sup>t</sup> PZH | Output enable time to high level                    | C <sub>L</sub> = 30 pF,<br>See Figure 1                 | R <sub>L</sub> = 75 Ω,  |     | 2.5 | 40  | ns   |

| <sup>t</sup> PZL | Output enable time to low level                     | C <sub>L</sub> = 30 pF,<br>See Figure 1                 | R <sub>L</sub> = 180 Ω, |     | 37  | 45  | ns   |

| <sup>t</sup> PHZ | Output disable time from high level                 | C <sub>L</sub> = 10 pF,<br>See Figure 1                 | S1 and S2 closed,       |     | 21  | 30  | ns   |

| tpLZ             | Output disable time from low level                  |                                                         |                         |     | 23  | 35  | ns   |

<sup>‡</sup> Not more than one output should be shorted at a time, and duration of the short circuit should not exceed one second.

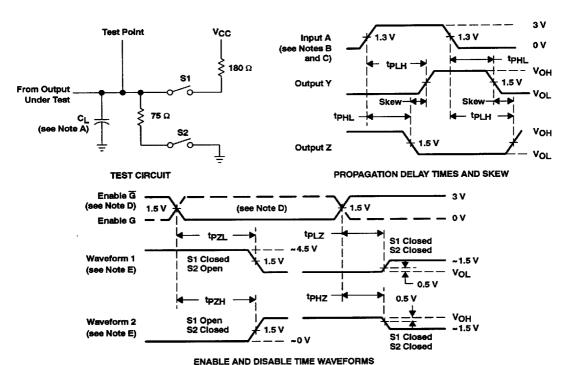

## PARAMETER MEASUREMENT INFORMATION

- NOTES: A. CL includes probe and jig capacitance. B. All input pulses are supplied by generators having the following characteristics: PRR ≤ 1 MHz, Z<sub>O</sub> ~ 50 Ω, t<sub>f</sub> ≤ 15 ns, and t<sub>f</sub> ≤ 6 ns.

- C. When measuring propagation delay times and skew, switches S1 and S2 are open.

- D. Each enable is tested separately.

- E. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

Figure 1. Test Circuit and Voltage Waveforms

2-16

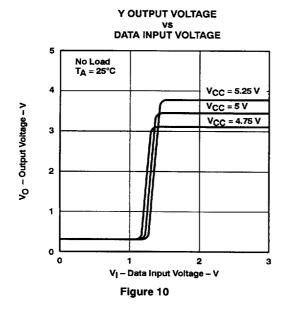

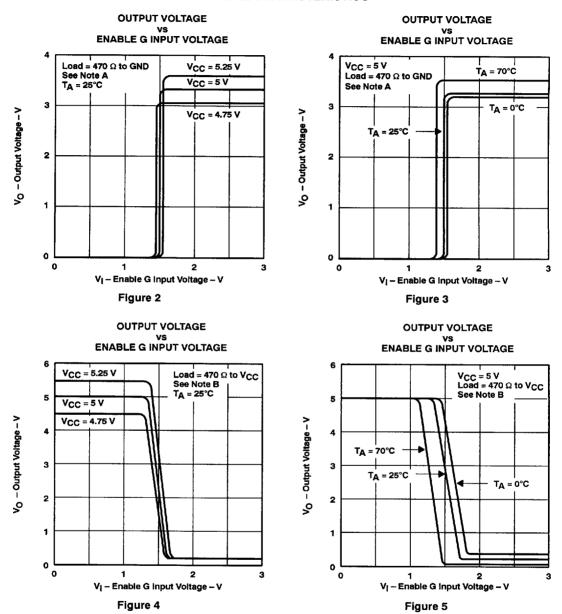

#### TYPICAL CHARACTERISTICS

NOTES: A. The A input is connected to V<sub>CC</sub> during the testing of the Y outputs and to ground during testing of the Z outputs.

B. The A input is connected to ground during the testing of the Y outputs and to V<sub>CC</sub> during the testing of the Z outputs.

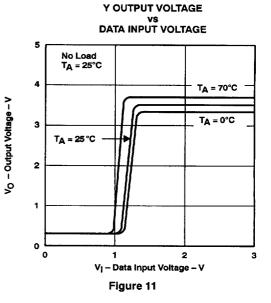

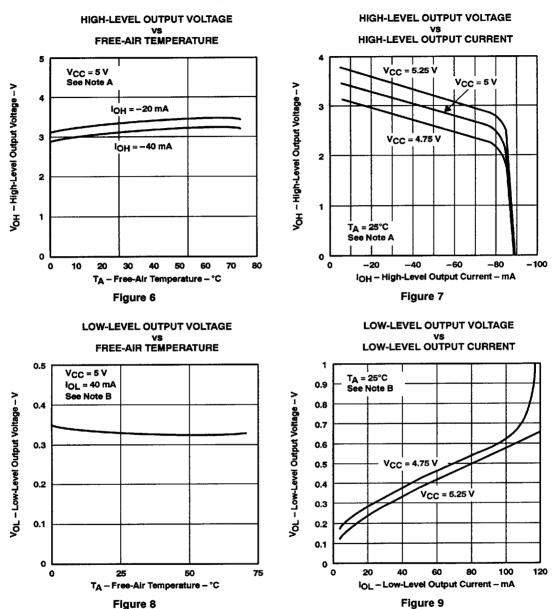

#### TYPICAL CHARACTERISTICS

NOTES: A. The A input is connected to V<sub>CC</sub> during the testing of the Y outputs and to ground during testing of the Z outputs.

B. The A input is connected to ground during the testing of the Y outputs and to V<sub>CC</sub> during the testing of the Z inputs.

8961724 0090262 T69 1

2-18

SLLS114 - D2433, JANUARY 1979 - REVISED MAY 1990

## **TYPICAL CHARACTERISTICS**